# Intelligent Manager Smart ACPI GPIO/SCI

#### **FEATURES**

- SMBus, version 1.0, Compliance

- Master mode function to interface with ACPI compliant embedded controller

- Support Pentium and x86-based designs

- Supported by default embedded controller firmware

- Accept up to 16 SCI inputs

- Programmable level or edge (falling and rising edge) triggered SCI inputs

- 20 possible edge-sensitive programmable General Purpose Inputs/Outputs per device

- Programmable addresses for cascading OZ992s

- 32KHz operating frequency

- Supports 3.3v or 5v supply

- LOW-power hardware-driven speaker alarm output

- Software programming kit available

- SMBALERT# and SMIEVENT outputs

- 8 programmable interrupt inputs for SMI event or SMBALERT#

- 8 Auto LED Flash(ALF) programmable outputs with 10% or 50% duty cycles

#### ORDERING INFORMATION

**OZ992S** - 28 pin SSOP

#### GENERAL DESCRIPTION

O<sub>2</sub>Micro's OZ992 Smart ACPI/SCI (System Control Interrupt) General Purpose Input/Output unit allows OEMs to transform their legacy systems to ACPI compliant systems by supporting up to 16 extra SCI inputs. Regular core logic chipsets, such as the Intel 430TX/BX and ACPI compliant embedded controllers have limited allowance for the GPIO or SCI input signals for the system. The OZ992 provides a bridge between the chipsets and the rest of the system to allow system designers a cost-effective way to improvise for such a deficiency.

OZ992 provides up to 20 GPIO signals in regular SMB slave mode. In addition, the OZ992 allows up to 16 System Control Interrupt (SCI) input transitions to be written to the system's embedded controller in master mode. The OZ992 provides the perfect solution for leading notebook vendors to stay ahead of the competition.

The OZ992 is an SMBus 1.0 compliant ACPI GPIO with 16 Programmable General Purpose I/Os pins flexible for a variety of functions such as programmable inputs/outputs, SMB/SMI interrupt service, power-saving, modularized hardware ID, and Auto LED Flash (ALF) status display. OZ992's other features include hardware-driven speaker alarm output.

As a Pentium and x86-based system compatible device, the OZ992 Smart ACPI GPIO is a highly cost-effective and practical solution for today's notebook and palmtop computers, pen-based data systems, personal digital assistants, and portable data-collection terminals.

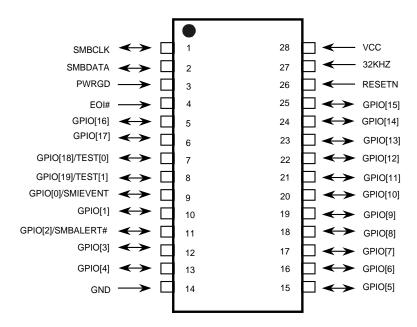

# **PIN DIAGRAM**

# **PIN DESCRIPTION**

| Name          | Pin No.                                                                                                                                                                                                                                                                                                                                | Type            | Input               | Drive                |            | Definition                                     |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|----------------------|------------|------------------------------------------------|--|

| SMBCLK        | 1                                                                                                                                                                                                                                                                                                                                      | i               | TTL                 | -                    |            | SMBus Clock Input                              |  |

|               | SMBus Clock Input for SMBus protocol communication.                                                                                                                                                                                                                                                                                    |                 |                     |                      |            |                                                |  |

| SMBDATA       | 2                                                                                                                                                                                                                                                                                                                                      | I/O             | TTL                 | 12mA                 |            | SMBus Data Input/Output                        |  |

|               | SMBus Dat                                                                                                                                                                                                                                                                                                                              | a Input/Outpu   | t for SMBus prot    | ocol communic        | cation.    |                                                |  |

| PWRGD         | 3                                                                                                                                                                                                                                                                                                                                      | I               | TTL                 | -                    |            | Host System Power Good                         |  |

|               |                                                                                                                                                                                                                                                                                                                                        |                 |                     |                      |            | ore Logic chipsets, is stable. Before the host |  |

|               | system's po                                                                                                                                                                                                                                                                                                                            | ower is stable  | , this input pin wi | Il tri-state all the | e output p | pins from OZ992.                               |  |

| EOI#          | 4                                                                                                                                                                                                                                                                                                                                      | I               | TTL                 | -                    |            | End of Interrupt                               |  |

|               |                                                                                                                                                                                                                                                                                                                                        |                 | 0 ,                 | OZ992 when the       | he activa  | ted SCI has been serviced. This pin is to be   |  |

|               | used with E                                                                                                                                                                                                                                                                                                                            | C master mo     | de only.            |                      |            |                                                |  |

| GPIO[17:16]   | [6:5]                                                                                                                                                                                                                                                                                                                                  | I/O             | TTL                 | 4mA                  |            | General Purpose I/Os                           |  |

|               | Fully programmable GPIOs that can be used for a variety of dedicated or specific functions. Pins GPIO[17:16] default as inputs. They are programmable to function as either GPI[17:16] inputs or GPO[17:16] outputs. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO Config. Tables (section 5.0) for input/output |                 |                     |                      |            |                                                |  |

|               |                                                                                                                                                                                                                                                                                                                                        |                 |                     |                      |            |                                                |  |

|               |                                                                                                                                                                                                                                                                                                                                        |                 |                     |                      |            |                                                |  |

|               | selections.                                                                                                                                                                                                                                                                                                                            |                 | 1                   | 1                    |            |                                                |  |

| GPIO[19:18] / | [8:7]                                                                                                                                                                                                                                                                                                                                  | I/O             | TTL                 | 4mA                  |            | General Purpose I/Os                           |  |

| TEST[1:0]     |                                                                                                                                                                                                                                                                                                                                        |                 |                     | <u> </u>             |            |                                                |  |

|               | Fully programmable GPIOs that can be used for a variety of dedicated or specific functions. Pins                                                                                                                                                                                                                                       |                 |                     |                      |            |                                                |  |

|               | GPIO[19:18]/TEST[1:0] default as inputs. They are programmable to function as either GPI[19:18] inputs or                                                                                                                                                                                                                              |                 |                     |                      |            |                                                |  |

|               | GPO[19:18] outputs. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO Config. Tables                                                                                                                                                                                                                                 |                 |                     |                      |            |                                                |  |

|               | (section 5.0) for input/output selections.                                                                                                                                                                                                                                                                                             |                 |                     |                      |            |                                                |  |

|               | During regular usage, pull-ups of $47K\Omega$ should be connected to GPIO[19:18]/TEST[1:0] to ensure the regular                                                                                                                                                                                                                       |                 |                     |                      |            |                                                |  |

|               |                                                                                                                                                                                                                                                                                                                                        | ration. Alterna | ative uses for Gi   | PIO[19:18] are       | as iESI    | [1:0], which provide 2 proprietary OZ992 test  |  |

|               | modes.                                                                                                                                                                                                                                                                                                                                 |                 |                     |                      |            |                                                |  |

| Name                  | Pin No.                                                                                                                                                                                                                   | Туре             | Input                    | Drive              |            | Definition                                                                               |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|--------------------|------------|------------------------------------------------------------------------------------------|--|--|--|

| GPIO[0]/              | 9                                                                                                                                                                                                                         | I/O              | TTL                      | 4mA                |            | General Purpose I/O /                                                                    |  |  |  |

| SMIEVENT              | Fully programmable GPIOs that can be used for a variety of dedicated or specific functions. Pin GPIO[0] has                                                                                                               |                  |                          |                    |            |                                                                                          |  |  |  |

|                       | SMIEVENT output as an alternate function. GPIO[0] defaults. It is also programmable to function as GPI[0]                                                                                                                 |                  |                          |                    |            |                                                                                          |  |  |  |

|                       | input, GPO[0]output, ALF[0] output, or ID[0] input. Refer to GPIO Config.1&2 Registers for more details and                                                                                                               |                  |                          |                    |            |                                                                                          |  |  |  |

|                       | GPIO Config. Tables (section 5.0) for input/output selections.                                                                                                                                                            |                  |                          |                    |            |                                                                                          |  |  |  |

| GPIO[1]               | 10                                                                                                                                                                                                                        | I/O              | TTL                      | 4mA                |            | General Purpose I/O                                                                      |  |  |  |

|                       | Fully progra                                                                                                                                                                                                              | mmable GPIO      | that can be us           | ed for a variety   | of dedica  | ted or specific functions. GPIO[1] pin defaults                                          |  |  |  |

|                       | as input. It is                                                                                                                                                                                                           | s also program   | nmable to funct          | ion as GPI[1] ir   | nput, GPC  | D[1]output, ALF[1] output, or ID[1] input. Refer                                         |  |  |  |

|                       |                                                                                                                                                                                                                           | onfig.1&2 Reo    | gisters for mo           | re details and     | GPIO C     | Config. Tables (section 5.0) for input/output                                            |  |  |  |

| 2012121               | selections.                                                                                                                                                                                                               |                  |                          |                    |            |                                                                                          |  |  |  |

| GPIO[2]/<br>SMBALERT# | 11                                                                                                                                                                                                                        | I/O              | TTL                      | 4mA                |            | General Purpose I/O /                                                                    |  |  |  |

| SWIBALER I#           | Fully progra                                                                                                                                                                                                              | mmahla CDIO      | that ass have            | ad for a variety   | of doding  | SMBALERT#                                                                                |  |  |  |

|                       |                                                                                                                                                                                                                           |                  |                          |                    |            | ted or specific functions. Pin GPIO[2] defaults n, can generate the SMBALERT# interrupt. |  |  |  |

|                       |                                                                                                                                                                                                                           |                  |                          |                    |            | Host which can be generated by all devices                                               |  |  |  |

|                       |                                                                                                                                                                                                                           |                  |                          |                    |            | grammable to function as either GPI[2] input,                                            |  |  |  |

|                       |                                                                                                                                                                                                                           |                  |                          |                    |            | fig.1&2 Registers for more details and GPIO                                              |  |  |  |

|                       | Config. Tabl                                                                                                                                                                                                              | es (section 5.0  | ) for I/O select         | ions.              |            |                                                                                          |  |  |  |

| GPIO[7:3]             | [17:15],                                                                                                                                                                                                                  | I/O              | TTL                      | 4mA                |            | General Purpose I/Os                                                                     |  |  |  |

| <u>.</u>              | [13:12]                                                                                                                                                                                                                   | l<br>mmahla GDIC | l<br>Se that can be      | used for a var     | iety of de | I<br>edicated or specific functions. GPIO[7:3] pins                                      |  |  |  |

|                       |                                                                                                                                                                                                                           |                  |                          |                    |            |                                                                                          |  |  |  |

|                       | default as inputs. They are programmable to function as GPI[7:3] inputs, GPO[7:3] outputs, ALF[7:3] outputs, or ID[7:3] inputs. Refer to GPIO Config.1&2 Registers for more details and GPIO Config. Tables (section 5.0) |                  |                          |                    |            |                                                                                          |  |  |  |

|                       |                                                                                                                                                                                                                           | put selections.  |                          | J                  |            | ,                                                                                        |  |  |  |

| GPIO[15:8]            | [25:18]                                                                                                                                                                                                                   | I/O              | TTL                      | 4mA                |            | General Purpose I/Os                                                                     |  |  |  |

|                       | Fully progra                                                                                                                                                                                                              | mmable GPIC      | s that can be            | used for a varie   | ety of dec | licated or specific functions. Pins GPIO[15:8]                                           |  |  |  |

|                       | default as inputs. Pins GPIO[15:8] as inputs are programmable to generate SMI/SMB interrupts. They are also                                                                                                               |                  |                          |                    |            |                                                                                          |  |  |  |

|                       |                                                                                                                                                                                                                           |                  |                          |                    |            | uts. Refer to GPIO Config.1&2 Registers for                                              |  |  |  |

| RESETN                | 26                                                                                                                                                                                                                        |                  | onfig. Tables (se<br>TTL | ection 5.0) for ii | ipui/outp  | Reset                                                                                    |  |  |  |

| KESEIN                |                                                                                                                                                                                                                           | ware reset Pi    |                          | OW) resets all     | registers  |                                                                                          |  |  |  |

|                       | OZ992 hardware reset. RESETN(active LOW) resets all registers to their default values. This pin is connected to the RC delay from the power supplied to OZ992.                                                            |                  |                          |                    |            |                                                                                          |  |  |  |

| 32KHz                 | 27                                                                                                                                                                                                                        | l I              | TTL                      | -                  |            | 32KHz Clock Input                                                                        |  |  |  |

|                       | 32KHz Cloc                                                                                                                                                                                                                | k Input.         |                          | ı                  |            |                                                                                          |  |  |  |

| GND                   | 14                                                                                                                                                                                                                        | GND              | -                        | -                  |            | Ground                                                                                   |  |  |  |

|                       | Ground.                                                                                                                                                                                                                   |                  |                          |                    |            |                                                                                          |  |  |  |

| VCC                   | 28                                                                                                                                                                                                                        | PWR              | -                        | -                  |            | 3.3V/5V Power Supply                                                                     |  |  |  |

|                       | 3.3V or 5V F                                                                                                                                                                                                              | Power Supply.    |                          |                    |            |                                                                                          |  |  |  |

# **GPIO Pins Alternate Usage**

| 19 | 16 15 | 8 7           | 0 |

|----|-------|---------------|---|

|    |       |               |   |

|    |       | GPIO[19:0]    |   |

|    | SMIEV | ENT/SMBALERT# |   |

**SCI to Embedded Controller**

# **DC CHARACTERISTICS**

### DC TABLE FOR VCC = $5.0V \pm 10\%$

| Symbol          | Parameter                     | Min | Max | Units |

|-----------------|-------------------------------|-----|-----|-------|

| Vcc             | Power Supply Voltage          | 4.5 | 5.5 | V     |

| V <sub>IH</sub> | Input HIGH Voltage            | 3.5 | -   | V     |

| VII             | Input LOW Voltage             | -   | 1.5 | V     |

| V <sub>OH</sub> | Output HIGH Voltage           | 2.4 | -   | V     |

| V <sub>OL</sub> | Output LOW Voltage            | -   | 0.4 | V     |

| I₁∟             | Maximum Input Leakage Current | -10 | 10  | μΑ    |

| I <sub>OL</sub> | Maximum Output Leakage        | -10 | 10  | μΑ    |

#### DC TABLE FOR VCC = $3.3V \pm 10\%$

| Symbol          | Parameter                     | Min | Max | Units |

|-----------------|-------------------------------|-----|-----|-------|

| V <sub>cc</sub> | Power Supply Voltage          | 3.0 | 3.6 | V     |

| V <sub>IH</sub> | Input HIGH Voltage            | 2.3 | -   | V     |

| VII             | Input LOW Voltage             | -   | 1   | V     |

| V <sub>OH</sub> | Output HIGH Voltage           | 2.4 | -   | V     |

| V <sub>OL</sub> | Output LOW Voltage            | •   | 0.4 | V     |

| I₁∟             | Maximum Input Leakage Current | -10 | 10  | μΑ    |

| l <sub>OL</sub> | Maximum Output Leakage        | -10 | 10  | μΑ    |

#### **CAPACITANCE**

| Symbol          | Parameter                  | 0 °C to 70°C | Units |

|-----------------|----------------------------|--------------|-------|

| C <sub>IN</sub> | Maximum Input Capacitance  | 10           | pF    |

| Соит            | Maximum Output Capacitance | 10           | pF    |

| C <sub>IO</sub> | Maximum I/O Capacitance    | 10           | pF    |

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol             | Parameter                                                 | Value                    | Units |

|--------------------|-----------------------------------------------------------|--------------------------|-------|

| V <sub>cc</sub>    | DC Power Supply Voltage                                   | 3.0 to 3.6               | V     |

| $V_{IN}, V_{OUT}$  | DC Input, Output Voltage                                  | $-0.3$ to $V_{DD} + 0.3$ | V     |

| I <sub>IN</sub>    | DC Current Drain V <sub>DD</sub> and V <sub>SS</sub> Pins | ±10                      | mA    |

| T <sub>STG</sub>   | Storage Temperature                                       | -40 to +125              | °C    |

| T <sub>OPER </sub> | Operation Temperature                                     | 0 to 70                  | °C    |

### **ICC SPECIFICATIONS**

| Symbol | Parameter      | Тур | Max | Units |

|--------|----------------|-----|-----|-------|

| Icc    | Supply Current | 50  | 60  | μΑ    |

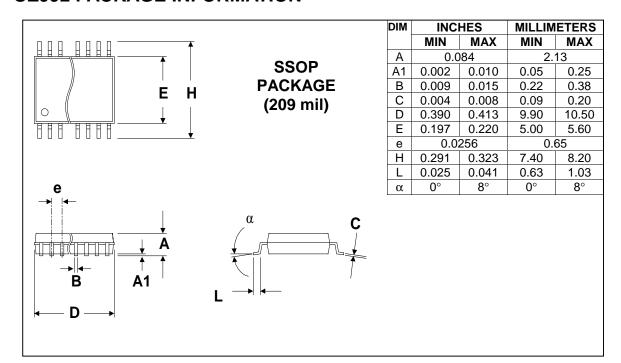

# **OZ992 PACKAGE INFORMATION**